O projeto da placa de circuito é uma tarefa crítica e demorada, e quaisquer problemas que surjam exigem que os engenheiros examinem todo o projeto, rede por rede, componente por componente. Pode-se dizer que o design da placa de circuito requer um nível de cuidado não inferior ao design do chip.

Um processo típico de projeto de placa de circuito consiste nas etapas a seguir.

As três primeiras etapas levam mais tempo, porque a verificação esquemática é um processo manual. Imagine uma placa SoC com 1000 ou mais conexões. A verificação manual de cada fio é uma tarefa longa e tediosa. Na verdade, é quase impossível verificar todos os fios, o que pode levar a problemas com a placa final, como fios errados, nós suspensos, etc.

A fase de captura esquemática geralmente enfrenta os seguintes tipos de problemas.

● Erros de sublinhado: por exemplo, APLLVDD e APLL_VDD

● Problemas que diferenciam maiúsculas de minúsculas: por exemplo, VDDE e vdde

● Erros de ortografia

● Problemas de curto-circuito do sinal

● E muito mais

Para evitar esses erros, deve haver uma maneira de verificar todo o esquema em poucos segundos. Este método pode ser implementado com simulação esquemática, o que ainda é raramente visto no processo atual de projeto de placas. A simulação esquemática permite que a saída final seja observada nos nós necessários, para que possa verificar automaticamente todos os problemas de conexão.

Isso é explicado abaixo com um exemplo de projeto.

Considere um diagrama de blocos típico de uma placa de circuito.

figura 1

Em um projeto de placa complexo, o número de conexões pode chegar a milhares, e um número muito pequeno de alterações provavelmente desperdiçará muito tempo para verificar.

A simulação esquemática não apenas economiza tempo de projeto, mas também melhora a qualidade da placa e aumenta a eficiência de todo o processo.

Um dispositivo típico sob teste (DUT) tem alguns dos seguintes sinais.

Figura 2

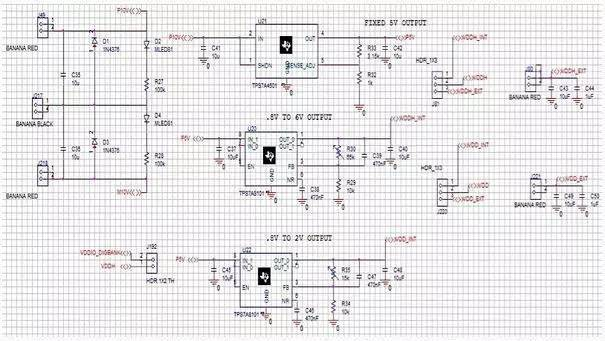

O DUT terá vários sinais após alguns pré-ajustes e possui vários módulos, como reguladores, amplificadores operacionais, etc., para ajuste de sinal. Considere um exemplo de um sinal de alimentação obtido através de um regulador de tensão.

Figura 3: Esquema da placa de amostra.

Para verificar as relações de conexão e realizar uma verificação geral, a simulação esquemática é usada. A simulação esquemática consiste na criação do esquemático, criação do testbench e simulação.

Durante a criação do banco de teste, um sinal de excitação é fornecido às entradas necessárias e, em seguida, os resultados de saída são observados no ponto de interesse do sinal.

O processo acima pode ser implementado conectando sondas aos nós a serem observados. As tensões dos nós e formas de onda podem indicar se o esquema tem erros ou não. Todas as conexões de sinal são verificadas automaticamente.

Figura 4: Testes esquemáticos e valores de simulação para cada nó.

Vejamos uma parte do diagrama acima, onde os nós e as tensões sondadas são claramente visíveis.

Assim, com a ajuda da simulação, podemos observar diretamente os resultados e confirmar se o esquema da placa está correto. Além disso, a investigação de alterações de projeto pode ser alcançada ajustando cuidadosamente o sinal de excitação ou os valores dos componentes. Assim, a simulação esquemática economiza muito tempo para os projetistas e verificadores de placas e aumenta as chances de correção do projeto.

O artigo é reproduzido da rede, se houver alguma infração, entre em contato conosco para excluir, obrigado.